汽车级晶振

单端

差分

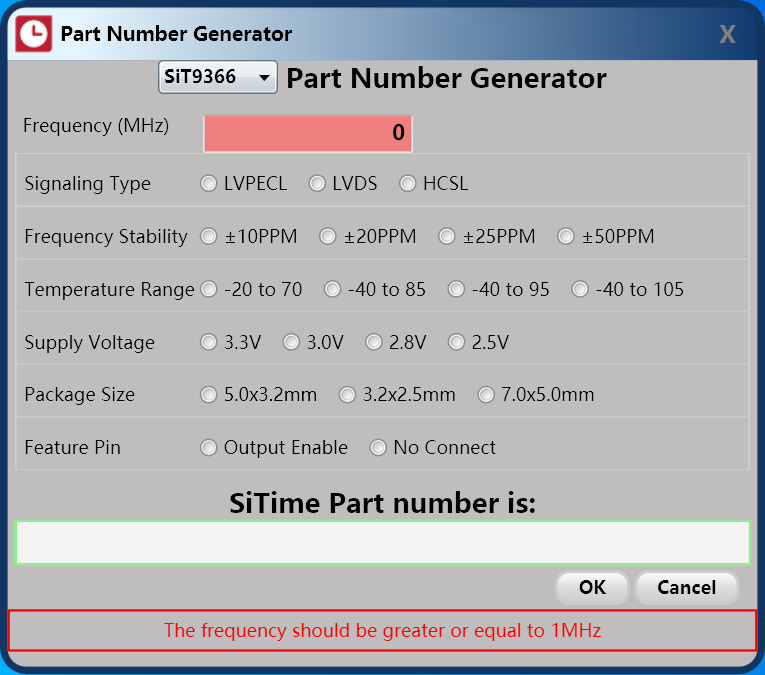

SiT9386

1-220MHz任意频率,AEC-Q100,汽车级差分晶振LVPECL/LVDS/HCSL

SiT9387

-40~105℃,220-725MHz任意频率,LVDS/LVPECL/HCSL差分信号

SiT9396

-40~125℃,1-220MHz任意频率,LVDS/LVPECL/HCSL差分信号

SiT9397

-40~125℃,220-920MHz任意频率,LVDS/LVPECL/HCSL差分信号压控晶振VCXO

单端

0.23ps低抖动差分

SiT3372

1-220MHz任意频率,HCSL/LVDS/LVPECL,最大±3200ppm牵引范围

SiT3373

220-725MHz任意频率,HCSL/LVDS/LVPECL,最大±3200ppm牵引范围低成本差分

高精度温补晶振TCXO

±0.5ppm~2.5ppm

±0.1ppm~0.25ppm

SiT5501

1-60MHz任意频率,±0.01ppm高精度,支持压控、数控、方波、削峰正弦波多种功能可选±5ppm温补差分

SiTime单端振荡器驱动单个或多个负载的建议

1. 介绍

具有快速边沿的时钟信号在印刷电路板(PCB)上作为传输线而不是简单的线连接。 如果PCB迹线的长度超过一定的极限它需要跟踪阻抗的一个或两个的源和负载阻抗的匹配。 阻抗不匹配导致信号反射来回传输线路,导致信号失真,如振铃,过冲和下冲。 本应用笔记提供了正确终止主要采用LVCMOS输出驱动的单端跟踪的指导原则。本文档讨论了单负载以及多负载情况。

2.集中与分布式PCB走线

如果响应于输入信号,所有点与均匀电位反应,时钟源,PCB走线和时钟接收器被认为是集总系统。 如果响应沿着跟踪分布,则系统称为分布式系统。 任何环境中的信号传播速度受到限制,因此无法完美集中系统。 通常的做法是将PCB走线的长度与最快的时钟信号边沿的有效长度进行比较,并使用该比率来判断系统是否可以被视为集总系统。 轨迹中的有效信号边沿长度计算为:

公式图片1

其中l =上升沿的长度,in。

Tr = 10% - 90%上升时间,ps

Tpd =每单位长度的传播延迟,ps / in。

例如,FR4 PCB走线中的传播延迟范围为140至180 ps / in。 假设Tpd = 150 ps / in。 1 ns上升沿的有效长度为6.7 in。

如果PCB走线的长度小于或等于信号边缘的有效长度的六分之一(1/6),则电路大部分以浅色的方式起作用。 当比较20%至80%的上升/下降时间时,更合适的配给是1/4以决定轨迹是否可以被视为集总元素。 集总电路不需要终止。 例如,假设1 ns上升时间为10%-90%,FR4 PCB材料走线长度大于1.1 in的时钟信号必须视为传输线。

SiTime振荡器的不同负载选项和驱动强度设置的上升和下降时间表可用于大多数部件系列的数据表。 当使用公式1时,从数据表上升/下降时间表(通常为5 pF)选择最低负载选项,因为接收机侧的容性负载不会影响驱动传输线时的源极上升/下降时间。

当时钟驱动器向传输线路发送边沿时,边缘在一段延迟之后到达负载。 如果负载(Z1)的阻抗与传输线(Zo)的阻抗不同,则信号的一部分从负载朝向源反射。源处的不匹配导致反射信号的一部分反射回负载( 圆头反射)。 反射信号的分数由反射系数[附录B]决定。 以下部分描述了终止策略,可用于在驱动单个或多个负载时最小化反射并提高信号完整性。

3.时钟终止建议

本节介绍常用的源终止策略。

3.1驱动单负载的源端接

图1:串联终止

串联端接是通过将跟踪线串联插入电阻来构造的源(见图1)。 适合阻抗匹配的输出阻抗时钟驱动器加串联终端电阻应等于跟踪阻抗,即:

公式图片2

其中Rs - 终端电阻的值

Rd - 驱动器的输出阻抗

Z0 - 传输线阻抗

作为示例,我们计算适用于具有默认驱动强度的SiT8208器件的终端电阻的值,并在3.3V下工作,驱动60Ω迹线。 从产品数据表[2]表4,我们确定默认驱动强度代码为“F”。 使用附录C中的表1,我们确定驱动强度代码为“F”和3.3V工作电压的SiT8208器件的典型输出阻抗为15.3Ω。 将跟踪阻抗和输出阻抗代入公式2,我们计算源终端电阻值Rs = 60Ω- 15.3Ω= 44.7Ω。

通过图1中的配置,来自源的信号将沿着轨迹行进,直到达到负载。 典型负载具有非常高的输入阻抗(在兆欧姆的范围内),所以不会吸收能量,并且整个信号被反射回到源。 因为源极处的阻抗与传输线的阻抗匹配,所以不会发生进一步的反射。 有关串联终端传输线中信号传播的详细图,请参见附录A。

SiTime建议使用SiTime提供的振荡器IBIS模型来模拟布局。 如我们使用Altium Designer软件中的Signal Integrity Analysis工具进行模拟SiT8208振荡器驱动5英寸60Ω传输线。 图2显示信号波形在负载侧模拟。 选择端接电阻Rs = 43Ω以匹配60Ω线路阻抗。 使用相同的终端电阻值来模拟+/- 10%的跟踪阻抗因此考虑到PCB制造的差异。

图2:Altium Designer仿真波形,SiT8208驱动负载通过5路传输线。 跟踪阻抗 - 54,60和66Ω,电源电压 - 3.3 V,源极端接 - 43Ω负载电容 - 5 pF。

有关SiTime单端的典型输出阻抗的信息,请参见附录C.振荡器。

3.2驾驶多个负载

PCB上的两个或更多个IC可能需要相同频率的输入时钟。 一种方法使用时钟驱动多个负载是使用扇出缓冲器,这需要额外的电路板空间和力量。 另一种方法是将一个输出连接到多个负载。

将一个输出连接到多个负载的首选方式是路由单个传输线尽可能靠近负载,并使用星形连接具有短迹的负载连接,因此负载被认为在跟踪结束时集中(3.2.1)。 这个方法要求负载彼此足够接近。

如果负载彼此太远,以便能够使用集中负载配置,那么在下面某些条件可以使用一个输出来驱动两条传输线分开负载(3.2.2)。 该配置要求输出驱动器具有更高的电流驱动能力而不是用于驱动单根传输线,不推荐与1.8V版本一起使用SiT1602等器件在使用60Ω和更低阻抗时列于表2传输线。 推荐使用IBIS模型运行信号完整性仿真将此配置结合到设计中。

一些驱动程序可能没有足够的驱动能力来处理两条传输线。 如果振荡器输出和负载之间的距离足够小,星形拓扑可能是考虑(3.2.3)。

典型振荡器的输出驱动器不够强大,无法驱动三个或更多的传输具有可在PCB(50 - 60Ω)上轻松设计的迹线阻抗的线。SiTime公司不建议从单个驱动程序驱动三条或更多条传输线。

3.2.1在轨迹结束时驱动多个负载集中

驱动多个负载的最简单的方案是当负载在灯的末端点亮时传输线(图3)。 如果负载可以放置得足够靠近,可以实现传输线的端部,使得将每个负载连接到传输线的迹线是不超过信号边缘有效长度的六分之一。 负载必须是以“星形”形式连接,如图3所示。串联终端电阻的值为以与单个负载情况相同的方式计算(公式2)。

图3:跟踪结束时多个负载集中的串联终端

图4说明了图3中的SiT8208-3.3V振荡器提供Rs = 43Ω,CL = 5 pF,时钟接收器数量 - 2,存根长度0.5英寸(〜75ps)。 如果存根太长反射会导致信号完整性问题(见图5)。

图4:用于SiT8208的Altium Designer仿真波形(负载侧)驱动两个负载集中在5英寸的末端。 跟踪。 跟踪阻抗 - 60Ω,电源电压 - 3.3 V源端接 - 43Ω,负载电容 - 5 pF。

图5:用于SiT8208驱动两个负载的Altium Designer仿真波形(在负载侧)当司机的痕迹在2英寸后分解成两个3英寸。 每个连接到负载的部分。跟踪阻抗 - 60Ω,电源电压 - 3.3 V,源极端接 - 43Ω,负载电容 - 5 pF。

3.2.2从一个源驱动两条传输线

如果时钟接收器,时钟接收器可能不会被布置在集总负载配置中相距甚远。 在这种情况下,可以使用单独的传输线来传送信号到每个负载。 图6示出了可以用于驱动多个的配置源驱动器的源端接传输线。

图6:从一个源驱动多条传输线

这种方法是低成本的,因为它每个迹线只需要一个终端电阻,并提供完整的在负载侧的摆幅信号振幅。 满足以下条件为最佳信号完整性[1]:

1. 时钟驱动器可以在边缘传输期间提供足够的峰值电流

2. 所有的传输线都具有相同的长度

3. 每个接收机侧的电容负载大致相同

4. 端接电阻由公式3计算

公式图片3

其中Rs源端接电阻,

Z0 - 传输线阻抗,

Rd - 驱动器输出电阻,

N - 驱动线数。

图7显示了图6中SiT8208-3.3V方案的Altium Designer仿真结果振荡器。 源端接电阻根据等式3计算上升沿之后和小凸起发生后的下降缘主要是由于寄生导致轻微阻抗失配的负载和源极驱动器电容。

图7:Altium Designer仿真波形(在负载端)为SiT8208驱动两个5-in。传输线。 跟踪阻抗 - 60Ω,电源电压 - 3.3 V,Rs = 15Ω,CL = 5 pF

驱动两条50Ω传输线需要比驱动两条60Ω线更强的驱动器。图8显示了使用相同方案的图6中的方案的Altium Designer仿真结果SiT8208-3.3V振荡器,但驱动两个50Ω线。 源端接电阻设置为零,但仍然源阻抗太高,无法确保像以前那样良好的信号完整性建议为SiT8208选择更强的驱动强度选项振荡器比用于模拟的默认驱动强度。

图8:Altium Designer仿真波形(负载侧)为SiT8208驱动两个5-in。传输线。 跟踪阻抗 - 50Ω,电源电压 - 3.3 V,Rs = 0Ω,CL = 5 pF

用单个源驱动两条传输线的方法确保信号从负载反映出来,它们之间的相互作用是相互抵消的其他和没有信号反映回负载。 从两个负载反射的信号都可以返回资源。 在源头上,他们再次反思,并通过驾驶员进入另一方传输线。 如果来自一条线的反射被另一条线的耦合所取消

线路没有信号能量被发送回负载。 为了完美消除,反射信号必须同时到达源,并且必须具有相同的形状。 传输线必须具有相同的长度,并需要平衡负载。 图9显示了影响不平衡电容负载在两条线上,而图10显示了无与伦比的影响传输线长度。

图9:Altium Designer仿真波形(两个负载时)SiT8208驱动两个5-in。传输线在两个负载下的电容不平衡时。 跟踪阻抗 - 60Ω,电源电压 - 3.3 V,Rs = 15Ω,CL1 = 5 pF,CL2 = 10 pF。

图10:Altium Designer仿真波形(在两个负载下)为SiT8208驱动两个传输线长度不同。 跟踪阻抗 - 60Ω,电源电压 - 3.3 V,Rs = 15Ω,CL = 5 pF。

3.2.3驱动两个负载的星形拓扑

在某些情况下,当振荡器的驱动器不足以驱动两条传输线(输出阻抗太高)时,可以使用启动拓扑(图11)。 Rt电阻网络用作中间终端。 通常选择Rt的值等于传输线路阻抗(Z0 / 3)的三分之一,这样当从任何节点看时,三个Rt电阻器的星形连接阻抗为Z0 / 2。 具有Z0阻抗的两条传输线的并联连接具有Z0 / 2阻抗,因此当从点A(图11)朝向负载观察阻抗为Z0时,其等于从源看的阻抗。 点A中的阻抗匹配,因此在那里不发生反射。

图11:驱动两个负载的星形拓扑

星形拓扑通常用于负载终止。 在这种情况下,从源极驱动器传播的信号通过迹线分离点而不反射,达到负载,并且由于负载阻抗匹配不反映回源。 负载看到一个没有反射的良好信号,但是非常低的振幅,这对于许多时钟接收器是不可接受的。

如果没有负载终止并且负载是高阻抗,则所有信号能量反射回到源。 使用Rt网络对中点的阻抗进行匹配,但是两个反射信号同时返回,因此发生耦合。 这使得很难在反射和耦合之间找到平衡,并实现可接受的信号完整性。

在无负载终止的情况下,不建议将该方法用于长于轨迹中边缘长度三分之一的传输线(见公式1)。 例如,对于1 ns的上升时间信号,星形段的长度不应超过2英寸。应使用IBIS模型对典型和拐角情况进行设计,以确保没有信号完整性问题。图12显示了模拟结果 具有短2-in的星形拓扑的拐角情况。痕迹。

图12:使用星型拓扑驱动两条传输线的SiT8208跨角的Altium Designer仿真波形(温度,电源电压和工艺)(图11)。 迹线阻抗 - 60Ω,迹线段长度 - 2 in。额定电源电压 - 3.3 V,Rs = 10Ω,Rt = 10Ω,CL = 5 pF。

图13和图14显示了模拟结果,说明信号波形如何随Rt和Rs分别变化。

图13:使用星型拓扑驱动两条传输线的SiT8208的Rt值范围的Altium Designer仿真波形(在负载侧)(图11)。 跟踪阻抗 - 60Ω,迹线段长度 - 2 in。,电源电压 - 3.3 V,Rs = 10Ω,CL = 5 pF。

图14:使用星形拓扑驱动两条传输线的SiT8208的Rs值范围的Altium Designer仿真波形(在负载侧)(图11)。 跟踪阻抗 - 60Ω,迹线段长度 - 2 in。,电源电压 - 3.3 V,Rt = 10Ω,CL = 5 pF。

如果需要更长的走线,增加信号上升/下降时间并不是一个问题,那么可以在Rs和传输线之间的源处使用额外的电容器(Cs),从而产生具有时间常数的低通RC滤波器的( Rs+Rd ) × Cs。 图15说明了如何在源极上使用15 pF电容可以驱动具有5 in.segments的星形迹线拓扑。

注意,在示例中说明星形拓扑的示例中的上升沿和下降沿的形状不适合于一些抖动敏感的应用。

图15:使用星形拓扑驱动两条传输线的SiT8208跨工艺角的Altium Designer仿真波形(在负载侧)(图11)。 源处附加的15 pF电容用于减慢信号边沿。 跟踪阻抗 - 60Ω,跟踪段长度 - 5 in。,电源电压 - 3.3 V,Rt = 10Ω,CL = 5 pF。

3.3使用源端接时的低通滤波效果

信号源与源终端一起驱动传输线,并将边缘发送到传输线。 在行尾,负载不会看到产生边沿的驱动器,而是传送线路。 传输线用作远端负载的驱动器,因此从负载的角度来看,驱动阻抗等于线路阻抗。

典型IC的时钟输入的负载大多是电容性的。 驱动阻抗正在形成一个低通滤波器,其负载阻抗看起来像一个简单的RC滤波器。 这种滤波器的截止频率为Z0CL。 假设50Ω传输线形成了一个角频率为637 MHz的低通滤波器。

对于大多数应用,该滤波器的转角频率足够高,不会导致信号衰减。 然而,用户必须密切监视负载电容,以确保转角频率保持舒适地高于时钟的工作范围。

请升级

400-888-2483

400-888-2483 我的账户

我的账户