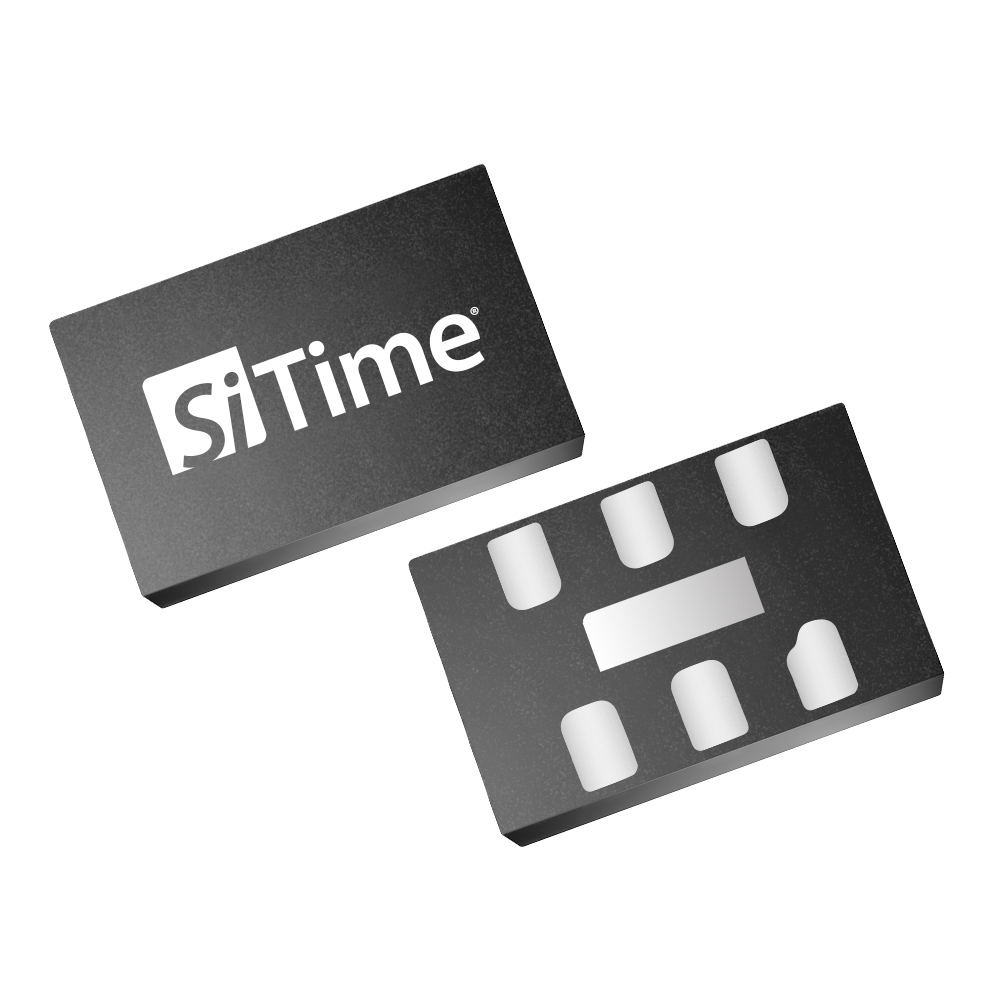

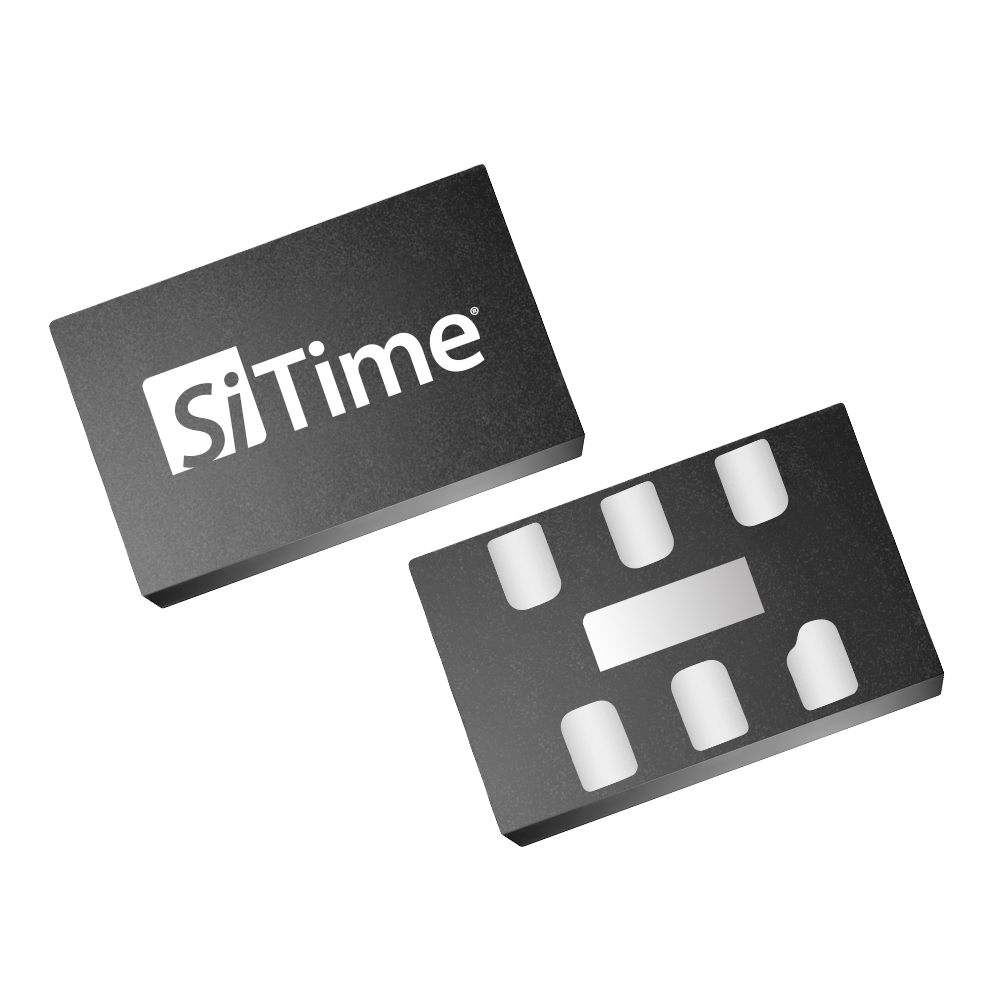

FPGA参考设计推荐差分晶振选型

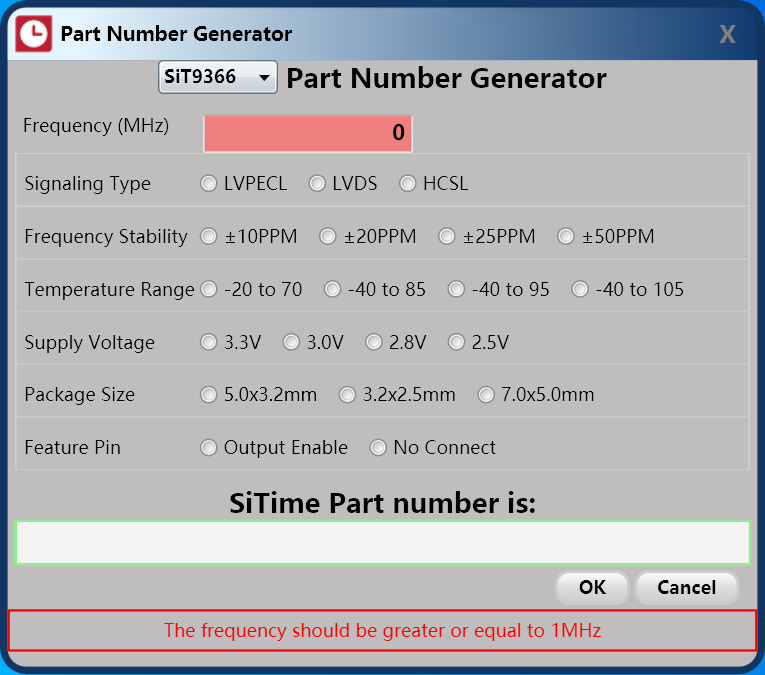

SiTime FPGA参考设计推荐差分晶振,支持CML/HCSL/LVDSLVPECL输出信号类型,支持1-625MHz区间频率,RMS相位抖动为0.6 ps(典型值)。与基于石英或SAW的传统振荡器不同,SiTime差分晶振可提供电压,频率稳定性、和封装参数的任意可编程组合选项,缩短供货周期。

- 0.6 ps(典型值)积分RMS相位抖动(12 kHz至20 MHz)

- 对于最严格的应用(例如1至10GbE)具有出色的抖动容限

- 出色的频率稳定性,低至±10 ppm

- 更好的时序余量,可增强系统稳定性和鲁棒性

- 广泛的可编程性

- 电源电压为2.5 V和3.3 V

400-888-2483

400-888-2483 我的账户

我的账户